- HOME

- Products

- Soc Solution

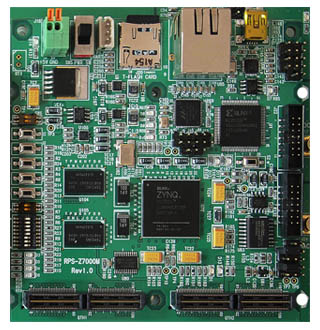

RPS-Z7020M

-

-

Dual Cortex-A9 Processor

Dual Cortex-A9 Processor DDR3, NAND/NOR, Gigabit Ethernet, SPI, USB, ADC, PCIe,

DDR3, NAND/NOR, Gigabit Ethernet, SPI, USB, ADC, PCIe,

UART, DMA, GPIO, AXI Bus Programmable Logic: 1.3million ASIC gates

Programmable Logic: 1.3million ASIC gates DDR3 Memory (1G-Bytes), SPI, NAND/NOR are included

DDR3 Memory (1G-Bytes), SPI, NAND/NOR are included Zynq7000 칩의 Programmable Logic 내에서 AXI Bus Prototyping

Zynq7000 칩의 Programmable Logic 내에서 AXI Bus Prototyping Tile Interface: RPS-7V2000TX, RPS-Zynq7000 Board 보드장착

Tile Interface: RPS-7V2000TX, RPS-Zynq7000 Board 보드장착 산업용 ARM Core Module

산업용 ARM Core Module

-